#### Advancement in Automated Simulation and Testing Technology for Safety-Critical Avionic Systems

Prof. Dr. Jan Peleska Dipl. Ing. Klemens Brumm Dipl. Ing. Gunnar Jonas Dipl. Inf. Tobias Hartmann

a (Verified Systems International GmbH) n (Airbus)

(RST Rostock System-Technik GmbH)

(TZI Center of Information Technology – University of Bremen)

#### Overview

**1.**Model-based simulation and testing:

Automated simulation, test case and test data generation from powerful specification formalisms

#### **2.**Large-scale simulation:

Integration of large simulation environments, consisting of parallel, possibly interacting, tasks

#### **3.**Hard real-time test-bench technology:

Scalable hard real-time execution platforms for the testing and simulation software

4.Conclusion and Background:

Research project KATO-TP13

#### **Objectives:**

Instead of manually programming explicit I/O sequences to be performed by simulation and test components ...

- ... generate simulation and test data from specifications in an automatic way

- ... perform on-the-fly checking of system under test behavior against specified expected results

#### **Objectives (continued):**

- Provide unified approach for simulation and testing on different levels:

- Software unit testing

- Software integration testing

- HW/SW integration testing

- System testing

- Wide area inter-site testing

- Allow for various specification styles made-to-measure for customers' needs and skills

#### Solutions:

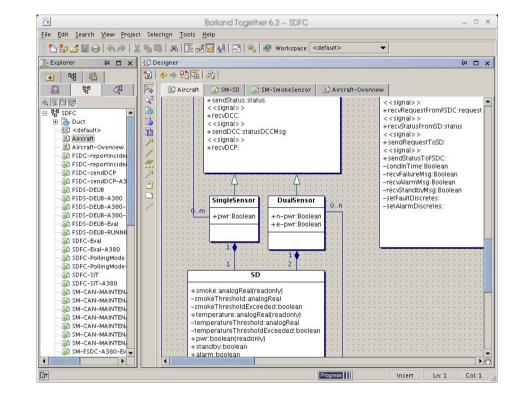

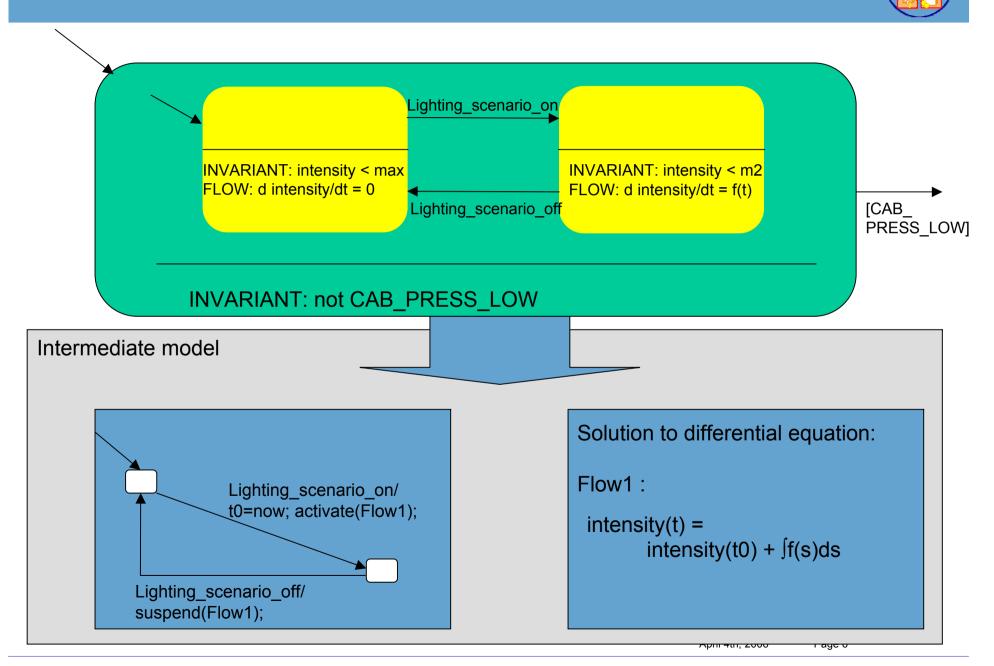

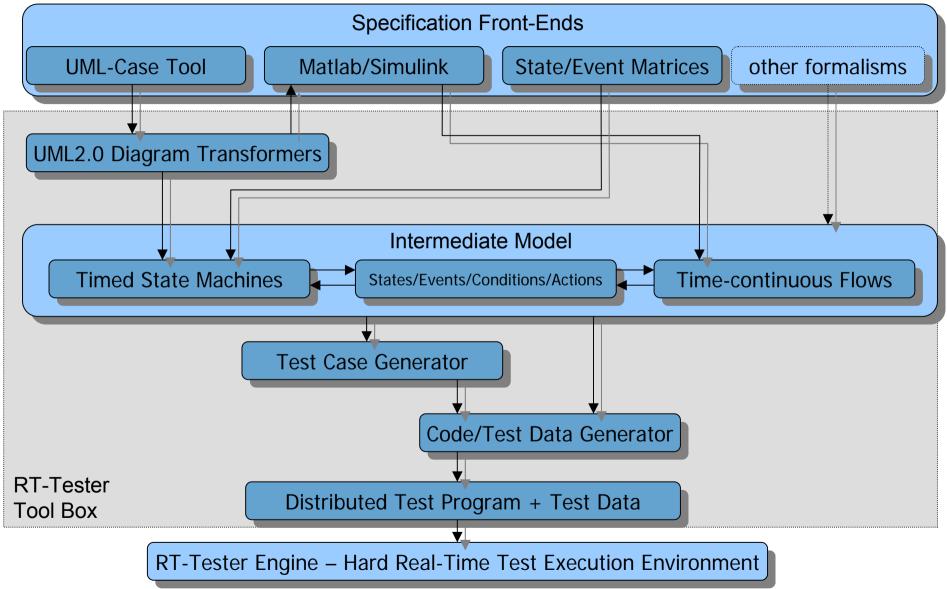

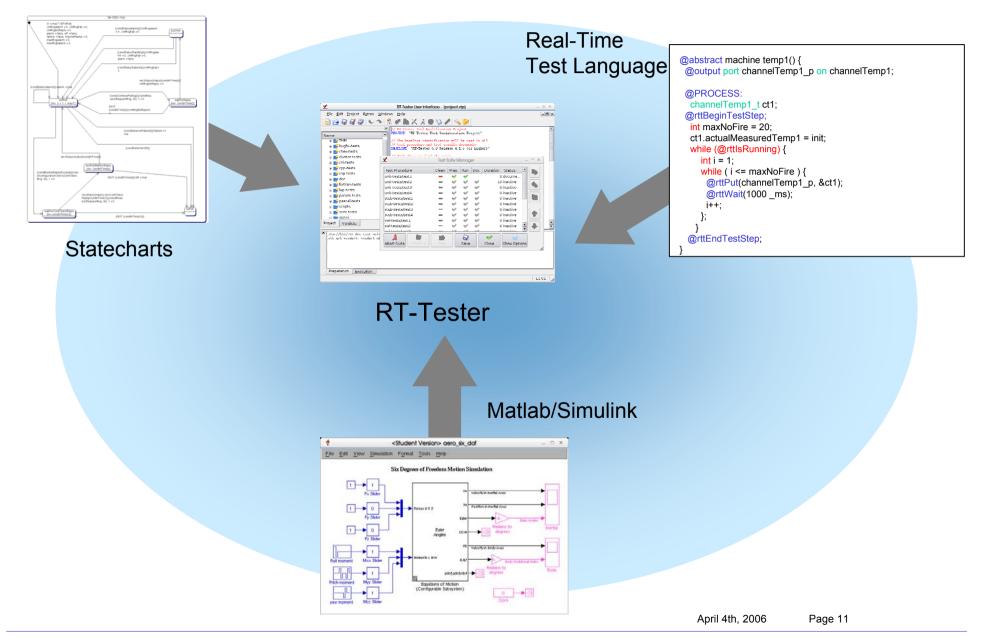

- Transform various specification formalisms to intermediate model representation

- Exercise test case generation algorithms on intermediate model

- Compile intermediate model into executable distributed simulation/test program plus test data

- All concepts implemented in RT-Tester Test Automation System

#### Part1 – Tool chain - overview

# **Objectives:**

- Integrate large numbers of simulations as parallel tasks in the testing and simulation environment

- Provide global access to simulation and test data to all components

- Distinguish between event- based and statebased – discrete and analog signal data

- Ensure execution in hard real-time

#### **Solutions:**

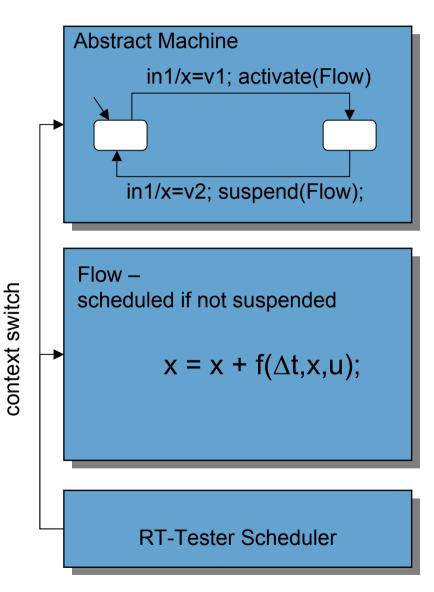

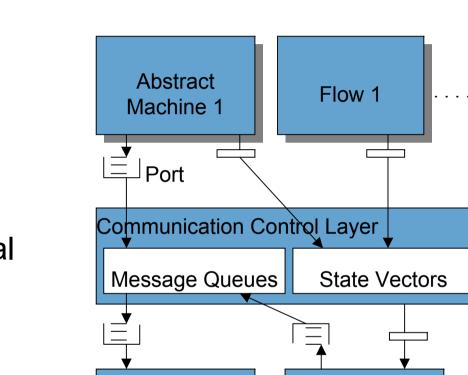

- Multi-threading architecture with highspeed context switching in user space

- Abstract Machines

encapsulate state based sequential

simulations as threads

- Flows encapsulate Δtintegration steps of time-continuous data changes as threads

#### Solutions:

- UML2.0 Statecharts simulations encapsulated in abstract machines – may activate and suspend flows as special actions

- Matlab/Simulink solutions of differential equations encapsulated in flows

- Customized simulations programmed in

- -Real-Time Test Language RTTL with

- –host language C/C++

- encapsulated in abstract machines or flows

- RT-Tester build tool integrates all simulations in one execution environment

Interface

Module 1

Transparent access to

events and state vectors within distributed system

Layered communication architecture

Part2 – Large scale simulation

- Message queues implement discrete

- events in time

Solutions:

Vectors implement global state components

> April 4th, 2006 Page 12

Hardware Interfaces

Interface

Module 2

#### Solutions:

- Universal port abstraction to access all types of interfaces

- Subscription mechanism for states and events provided by

- Simulations

- System Under Test (SUT)

- HW-in-the-loop components

- On-the-fly switching between

- -Simulation S providing state data x

- HW-in-the-loop original equipment E producing x

possible: S and E use equivalent ports

# Part3 – Hard real-time test bench technology

## **Objectives:**

- Develop novel test bench technology with

- scalable performance

- scalable number of interfaces

- guaranteed hard realtime properties

- modular architecture

# **Objectives (continued):**

- high degree of re-use for different systems under test

- optimized

cost/performance ratio

by combining off-the shelf components with

customized HW/SW

solutions

# KATO

# Concepts & solutions – HW: Scalable test engine power:

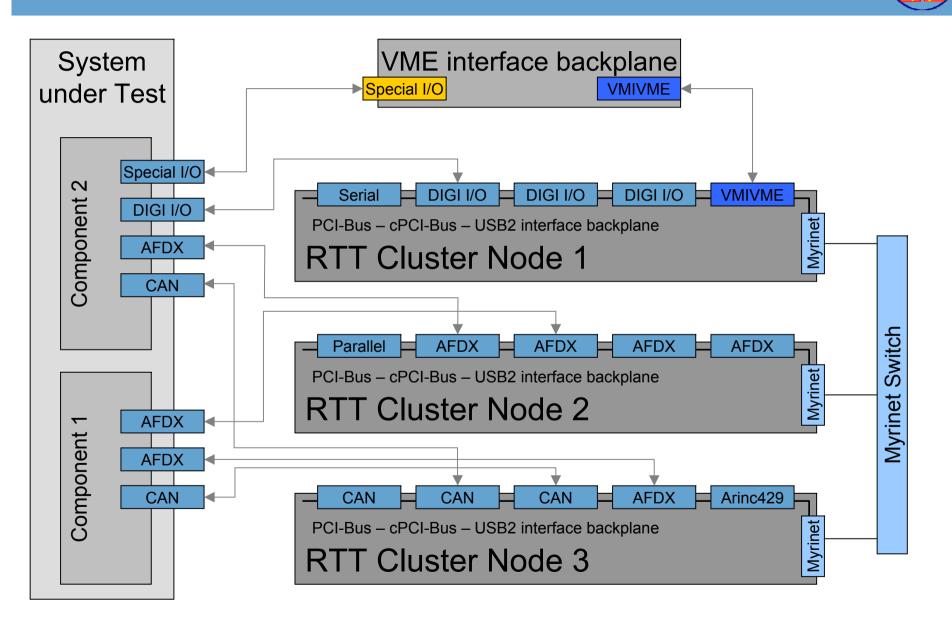

- Cluster architecture

- 2 or 4 CPU PC cluster nodes

- High-speed DMAbased cluster communication

#### Concepts & solutions – HW:

- Scalable test engine power:

- Distributed interface back-planes connected to different cluster nodes:

- PCI

- USB2

- CAN

- -VME

- cPCI

#### Concepts & solutions – Software:

Guaranteed hard realtime properties

- Hard real-time kernel extension for Linux

- Simulations and tests run on reserved CPUs

no interference from operating system

#### **Concepts & solutions – SW:**

- Guaranteed hard realtime properties

- Scheduling

precision < 3µs</li>

- ▶ Event communication

Simulation ↔ Interface

< 100µs</li>

- Standard software usable on nonreserved CPUs

#### Part3 – Hard real-time test bench technology

KAT

We have presented novel results on

- Model-based simulation and testing,

- Large-scale simulation,

- Hard real-time test-bench technology,

investigated within research project

KATO-TP13 – a project of the German LUFO III aerospace research program

#### **Conclusion and Background**

#### Research project KATO-TP13:

- Techniques for requirements validation by combined

- Structured reviews

- Simulation

- Model checking

- Exploitation of formally modeled domain knowledge from

- Aircraft domain (e.g. ATA chapters)

- Manufacturer's expertise (re-usable concepts)

for verification and testing of avionics systems

#### **Conclusion and Background**

- Research project KATO-TP13 (continued)

- Novel testing technology covering both

- Hardware test bench technology:

- Scalable performance

- Flexible test bench adaptation to different systems under test (SUT)

- Software for automated simulation and testing:

- Hard real-time platform for executing large networks of simulations

- Specification-based testing: automated test case generation and checking of SUT responses against specification models

#### **Conclusion and Background**

# • KATO-TP13 – cooperation partners:

Airbus, Hamburg

University of Bremen Center of Information Technology

RST Rostock System-Technik GmbH

Verified Systems International GmbH Bremen